本文由半导体产业纵横(ID:ICVIEWS)综合

中国本土半导体设备渐入佳境。

6月12日,华海清科宣布,其首台12英寸封装减薄贴膜一体机Versatile–GM300出机发往国内头部封测企业。

据介绍,封装减薄贴膜一体化设备Versatile–GM300是华海清科继在先进封装领域推出量产机型减薄抛光一体机(Versatile–GP300)之后,面向封装领域推出的又一关键核心产品。该设备全机采用新型布局,可灵活实现薄型晶圆背面超精密研削与干式抛光应力去除功能,搭配晶圆贴膜机联机使用,可为8/12英寸晶圆安全可靠地提供从精密减薄、清洗干燥到粘贴料环、背膜剥离的全流程自动作业,满足高端封装领域的薄型晶圆生产工艺技术需求。

华海清科表示,Versatile–GM300超精密晶圆减薄机,在技术上突破了超薄片减薄工艺技术壁垒,依托先进的厚度均匀性控制技术,可实现片内均匀性TTV<1.0μm,达到了国内领先和国际先进水平。该产品具有高精度、高刚性、工艺开发高灵活性等优点,可广泛应用于封装领域中的晶圆背面减薄、BG/DC倒膜等工艺。本次12英寸封装减薄贴膜一体机出机,将有助于进一步巩固和提升公司的核心竞争力。

晶圆背面研磨工艺

经过前端工艺处理并通过晶圆测试的晶圆将从背面研磨(Back Grinding)开始后端处理。背面研磨是一项关键工序,不仅旨在减小晶圆的厚度,还能有效解决前后两个工艺之间可能出现的问题。随着半导体芯片(Chip)厚度的减薄,我们能够实现更多芯片的堆叠(Stacking),从而提高集成度。然而,较高的集成度也可能带来产品性能的下降,因此,在集成度与产品性能之间存在一定的矛盾。因此,选择适当的晶圆研磨(Grinding)方法对于降低半导体芯片成本和确保产品质量至关重要。

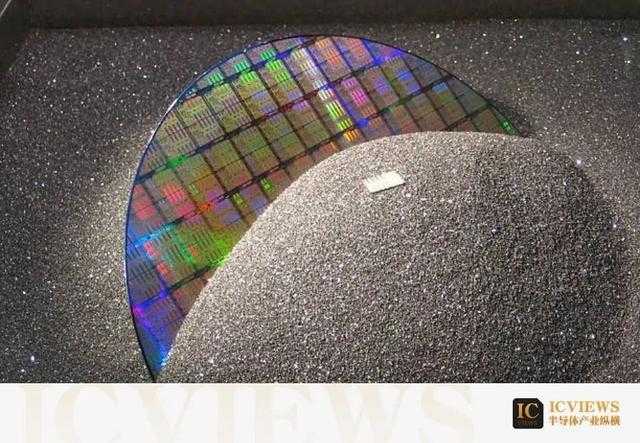

在半导体的制造过程中,晶圆的外观经历了多次变化。在晶圆制造工艺中,我们通常会对晶圆的边缘和表面进行抛光,这个过程会涉及研磨晶圆的两个面。当前端工艺完成后,我们可以进行背面研磨工序,仅研磨晶圆的背面。这个步骤旨在去除前端工艺中受到化学污染的部分,并减小芯片的厚度。这对于制造搭载在IC卡或移动设备上的薄型芯片非常适用。此外,背面研磨还具有降低电阻、减少功耗以及提高热导率并快速将热量散发至晶圆背面的优点。然而,由于晶圆较薄,很容易受到外力的影响而折断或翘曲,使得处理步骤变得更加困难。

背面研磨一般可分为以下三个步骤:首先,在晶圆上贴上保护胶带贴膜(Tape Lamination)。其次,研磨晶圆的背面。最后,在将芯片从晶圆中分离出来之前,需要将晶圆安置在预先贴有保护胶带的晶圆载片(Wafer Mounting)上。晶圆载片工艺通常作为分离芯片(切割芯片)的准备阶段,并可能与切割工艺同时进行。近年来,随着芯片的不断变薄,工艺顺序也可能发生改变,并且工艺步骤变得越来越精细化。

背面研磨的第一步是进行贴膜。贴膜是一种涂层工艺,将胶带粘贴在晶圆的正面。在背面研磨过程中,硅化合物会扩散到晶圆的四周,而晶圆也容易因外力而破裂或翘曲,尤其当晶圆面积较大时,这种情况更容易发生。因此,在进行背面研磨之前,我们需要在晶圆上贴上一层薄薄的紫外线(UV)蓝膜,以保护晶圆的表面。

在贴膜过程中,为了确保晶圆和胶带之间没有间隙或气泡,我们需要提高粘合力。然而,在背面研磨完成后,为了分离晶圆与胶带,我们需要通过紫外线照射降低胶带的粘合力。在剥离胶带后,不应该在晶圆表面留下胶带残留物。有时,我们也可以使用粘合力较弱且容易形成气泡的非紫外线减粘膜,尽管这种方法存在一些缺点,但价格相对较低。此外,我们还可以使用比UV减粘膜厚两倍的凸块(Bump)膜,在未来预计会得到越来越广泛的应用。

经过背面研磨后,晶圆的厚度通常会从800-700μm减少到80-70μm。将晶圆减至十分之一的厚度,可以实现四到六层的芯片堆叠。近年来,通过两次研磨的工艺,晶圆甚至可以减薄到约20μm,从而实现16到32层的多芯片封装(MCP)结构。尽管使用了多层结构,但为了确保成品封装的总高度不超过一定厚度,我们仍然追求更薄的晶圆。然而,晶圆越薄,其固有缺陷也就越多,下一道工序也会变得更加困难。因此,我们需要先进的技术来解决这些问题。

背面研磨技术的发展在于尽可能将晶圆切割得更薄,以克服加工技术的限制。对于厚度大于等于50μm的晶圆,通常有粗磨(Rough Grinding)和精磨(Fine Grinding)两个步骤,这两次研磨之后会进行切割和抛光等处理。与化学机械抛光(CMP)类似,通常会在抛光垫和晶圆之间使用浆料(Slurry)和去离子水(Deionized Water)。这种抛光工作可以减少晶圆和抛光垫之间的摩擦,从而使晶圆表面变得光滑。当晶圆较厚时,可以采用超精细研磨(Super Fine Grinding),但随着晶圆的变薄,需要进一步进行抛光。

如果晶圆变得越薄,在切割过程中容易出现外部缺陷。因此,对于厚度为50μm或更小的晶圆,我们可以改变工艺顺序,采用先切割再研磨的DBG(Dicing Before Grinding)方法。按照划片(Dicing)、研磨和再次划片的顺序,我们可以安全地将芯片从晶圆中分离出来。此外,还存在一种特殊的研磨方法,即使用坚固的玻璃板来防止晶圆破裂。

随着电子器件的小型化,对集成度的要求越来越高,背面研磨技术需要不断克服其局限性并持续发展。同时,我们不仅需要解决晶圆本身的缺陷问题,还必须为未来可能出现的新工艺问题做好准备。为了应对这些挑战,可能需要重新调整工艺顺序,引入半导体前端工艺中应用的化学蚀刻技术,并全面开发新的加工方法。为了解决大面积晶圆固有的缺陷,我们正在进行多种探索和试验,以改进研磨方法。此外,也正在研究如何回收和利用研磨晶圆后产生的硅渣。通过这些努力,我们致力于推动背面研磨技术的进步,以满足不断发展的电子工业的需求。

*声明:本文系原作者创作。文章内容系其个人观点,我方转载仅为分享与讨论,不代表我方赞成或认同,如有异议,请联系后台。

转载此文是出于传递更多信息目的。若来源标注错误或侵犯了您的合法权益,请与本站联系,我们将及时更正、删除、谢谢。

https://www.414w.com/read/724745.html