本文由半导体产业纵横(ID:ICVIEWS)编译自semi engineering

光子学和电子学这两个曾经分离的领域似乎正在趋于融合。

光学和电气领域正开始在更深层次上交叉,特别是在数据中心对3D-IC和AI/ML训练日益关注的情况下,推动了芯片设计方式及集成方法的变化。

这种转变的根源在于AI/ML的功耗、性能需求。现在,仅仅为了训练一个模型可能需要占用数据中心的多座大楼。这些性能需求,再加上数据中心本身的爆炸式增长——从独立建筑物发展为遍布数个电网的地理分布网络,需要专用光纤网络来处理大量带宽——要求光子学行业进行创新。

为了应对海量数据和不断扩展的网络基础设施,以太网速度正在迅速从 800 Gb/s 标准(IEEE P802.3df工作组于2024年2月批准)提高到 2026 年计划中的1.6Tb/s。与此同时,芯片架构师和工程团队正在努力减小系统延迟。但即便如此还不够,这就是光通信突然受到更多关注的原因。

十多年前,有人预测光学将在数据中心内变得至关重要。Alphawave Semi 首席技术官Tony Chan Carusone表示:“现在,有些人非常高兴地看到光学在一些大规模应用中占据了应有的位置——比如人工智能/机器学习等。” “我们所有人都在努力预测将得到广泛应用的技术,以及哪些方面需要开发更定制化的解决方案。”

一个主要的关注领域是电光开关技术。光学器件是长距离的最佳解决方案,正确调整的电子器件可以降低延迟和阻抗。二者结合在数据中心机架和集群中,使用带有电气线路的 ASIC 开关,从整个板面延伸到前面板,在前面板插入可插拔光学元件以执行电光转换及其反向操作。过去,这被认为是一种高效而优雅的解决方案,但所有这些毫米都会累加起来,使传统的系统架构不可持续。

“将来会有一个时间点,你的所有功耗都会被用来尝试在没有任何错误的情况下高效地将信号从A点传输到B点,”Ansys的首席研发工程师Ahsan Alam说道。“这就是所谓的‘功耗墙’。当你所有的功耗都用来将信号从一个芯片传输到另一个芯片时,你就没有剩余的功耗来执行CPU、GPU或ASIC中的实际计算。”

CPO和LPO

业界正在寻找解决功耗墙问题的不同方法。“一种方法是共同封装光学器件,”Synopsys 高速 SerDes IP 解决方案首席产品经理 Priyank Shukla 表示。“与其在表面积有限机架单元边缘进行电光转换(LPO),不如将光纤直接引入芯片封装中并在其中进行转换。”

尽管如此,可插拔器件与共封装光学器件 (CPO) 之间的争论仍在继续。一方面,有人主张采用简单易行且运行良好的传统系统,拥有长期建立的IEEE标准。另一方面,是一种较新的方法,采用最近批准的标准,可能提升性能并降低成本。

Broadcom光学系统市场和运营副总裁Manish Mehta表示:“共封装光学架构促进了ASIC与光学引擎在共同基板上的集成,并消除了信号传输到前端插拔式收发器所产生的信号损伤。由于CPO基板上的信号路径简化,通过移除光学DSP并在光学引擎中使用CMOS电子IC组件,光互连功耗减少了70%。”

与此同时,线性驱动光学器件已成为一种可能的独立选择,也是可插拔光学器件和共封装光学器件过渡的一种方式,ASIC而非DSP驱动光学器件。英伟达于 2023 年在 OIF 上首次提出了这一想法,迄今为止已经推出了许多变体,希望能够在降低功耗的情况下创建更快的连接。

“英伟达首席执行官黄仁勋在 GTC 主题演讲中指出,通过光子传输数据需要在光纤的一侧安装发射器,在另一侧安装接收器。黄仁勋谈到取消收发器并直接使用铜缆。”Ansys 战略合作伙伴总监 Rich Goldman 说道。“尽管光子学有诸多已知的优势,但这个想法可能也具有一定的价值,因为收发器需要进行一些工作,任何工作都可能减慢速度并增加功耗。这意味着我们需要从芯片一直讨论到整个系统,这些都是相互关联的。我们已经讨论了很长时间,现在我们已经实现了。”

随着设计的不断发展,当前的光学互连选择介于传统的可插拔式模块、CPO和线性驱动可插拔光学(LPO)之间,而LPO位于中间位置。对于那些还没有准备好完全过渡到 CPO 的人来说,LPO 的优势在于熟悉的外形尺寸,损失较少。

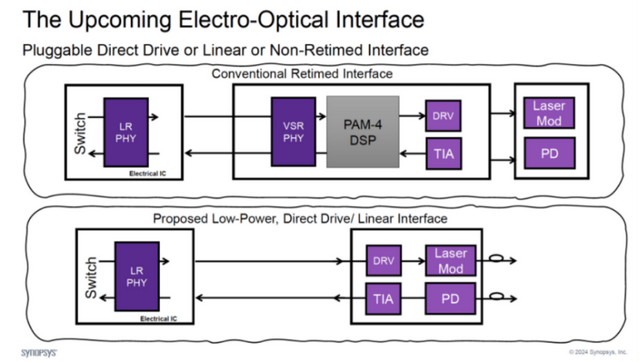

“这是新的低功耗互连,”Synopsys的Shukla说道。“Meta和其他超大规模网络服务提供商公开要求线性驱动技术,在电光转换中,你可以消除中间的再定时器,这样电驱动器直接驱动光学组件,这就是你在信号链电光转换中节省功耗的方式。但这也使得SerDes设计更加具有挑战性。”

图1:共封装光学与可插拔光学的插入损耗节约比较。Broadcom将线性驱动可插拔光学视为一个中间步骤。来源:Broadcom

LPOs是由交换机SerDes直接驱动的,没有再定时器。再定时器曾因通过创建新信号来延长传输距离而受到重视,它们增加了信号,但不会放大噪音,与再驱动器不同,后者会同时放大信号和噪音。但现在,它们的存在受到质疑,因为它们的功能会增加延迟并消耗额外的功耗。

Infinera的市场营销高级副总裁Rob Shore表示:“任何需要数字信号处理器的东西都需要功耗。”“对于数据中心运营商来说,特别是那些试图建立人工智能基础设施的运营商来说,最主要的问题是功耗。他们希望将每瓦功耗都用于服务器,尽可能少地用于光学设备。”

图2:无再定时器接口。来源:Synopsys

对于支持者来说,LPO 是功能性和熟悉度之间经过深思熟虑的折衷方案。“对于CPO,如果你从传统的可插拔式光学模块转向一种在实施方面看起来非常不同的技术,在可靠性方面不可避免会产生质疑,”Ansys的Alam说道。“LPO 仍将具有与当前可插拔设备相同的外形尺寸。这对于人们选择这条路线而不是选择CPO来说是一个很大的动机,因为后者将会有根本不同的变化。”

然而,LPO也有其自身的局限性。“你无法在非常长的距离上传输数据,”Alam解释道。“其传输距离远比CPO短。CPO未来也将提供更多的功耗优势。相反,LPO由于其模块化结构,将提供更优秀的可维护性。最终,一些团体会选择LPO,一些会选择CPO,还有一些会两者兼而有之。在一些情况下,如当前可插拔式收发器和LPO,可插拔式光学模块是有意义的,而在另一些情况下,CPO是有意义的。两者都将继续存在,并且市场份额将在两者之间划分。”

从设计的角度来看,CPO 和 LPO 面临的挑战有很好的重叠,并且应该主要由当前的 EDA 工具支持,尤其是 LPO,因为它与当前的可插拔收发器相似。Alam 指出:“您可以使用目前用于 LPO 可插拔收发器设计的相同解决方案,而对于 CPO,则有多物理场工作流程来应对新兴的封装挑战。”

散热问题

尽管CPO技术承诺降低功耗,但设计面临着热问题的挑战。但问题并不在于激光器。

“如果你担心热问题,那么‘激光’这个词听起来很可怕,”Alam说道。“但是对于共封装光学技术和芯片内外的激光器来说,大多数人将他们的光学引擎和激光器安装在单独的芯片上,然后将激光器带入共封装光学器件。保持激光器分离的优点是可以减少向开关系统产生的热量。此外,激光器对温度变化敏感,因此当你将其带入3D-IC时,需要考虑激光器的可靠性,因为存在热串扰等问题。因此,将激光器置于芯片外是一个更简单的解决方案。话虽如此,已经有一些解决方案将激光器集成到了共封装光学器件中。总的来说,无论使用片内还是片外的激光器,都需要对整个共封装光学器件进行热仿真,以减小热串扰、优化系统冷却,并降低工作温度,以确保性能和可靠性。”

热量是光子学中的一个大问题,但在电气IC中并不存在,因为它会影响信号完整性。虽然某些组件的行为可能对温度变化非常敏感,但电路通常具有反馈回路,可以调整热调谐器上的电压,从而调整设备温度和性能。然而,有些对温度变化敏感的元件不具备热调谐功能。

Ansys 的 Goldman 表示:“你必须非常注意热量及其对设计的影响。” “我们在数据中心更多地使用光子学,因为铜会升温,而玻璃不会,而且光还携带更多信号。你可以实现更大的带宽,而且速度是光速。它更好、更快、更便宜。”

简单来说,产生额外热量的不是激光器,而是封装结构。

“共封装对整个行业来说是一个挑战,”Shukla说道。“你必须使用共封装的部署模拟性能。每个人都在尽力解决这个问题。光子芯片提供商、光子晶片厂商正在开发这些工艺,以限制他们的光子组件、激光调制器的热耗散。EDA公司正在开发流程,允许系统设计人员建模温度分布,以便正确建模光学元件的性能。例如,如果激光器的性能随温度升高而变化,我们需要工具有效地模拟这一变化,并在数字方面采取措施来补偿性能的下降。这就是EDA工具和设计者正在解决的难题,而SerDes设计者则从电气方面降低功耗。”

然而,与电子学不同的是,在某些光子电路中,精确控制的热量被用来调节激光器,随着热量的增加,波长会发生变化。但是,这种特性可能会使热过载成为一个更加令人担忧的问题。

“很多结构都会内置加热器来调节其波导的谐振和滤波能力,”Keysight的业务发展、市场营销和技术专家Chris Mueth说道。“它需要有一个反馈环路。如果你要调谐到特定的波长,你就需要对此进行控制。当你开始在3D-IC中进行集成时,芯片自身会加热,问题就变得更加复杂了。”

情况复杂,但并非无望。“你需要考虑控制回路来处理这个问题。这并不是无法解决的事情,”Mueth说道。“这是当你在集成3D-IC和光子学以及所有这些带有物理效应的不同技术时,你必须处理的众多多学科特征之一。”

经过几十年的演示与讨论,光子学和电子学这两个曾经分离的领域似乎正在趋于融合。

“无论是共封装光学、可插拔光学还是单片集成,光子学在包括数据中心光学和高性能计算在内的广泛应用中与电子学越来越接近,”Synopsys的EDA团队产品营销负责人Jigesh Patel说道。“这一趋势需要在设计创新上进行范式转变——从SoC转向片上系统方法,其中在通用电子光子设计自动化环境中多种技术的协同设计和协同优化是商业成功的关键。”

*声明:本文系原作者创作。文章内容系其个人观点,我方转载仅为分享与讨论,不代表我方赞成或认同,如有异议,请联系后台。